# Hibernus: Sustaining Computation during Intermittent Supply for Energy-Harvesting Systems

Domenico Balsamo, Alex S. Weddell, *Member, IEEE*, Geoff V. Merrett, *Member, IEEE*, Bashir M. Al-Hashimi, *Fellow, IEEE*, Davide Brunelli, *Member, IEEE*, and Luca Benini, *Fellow, IEEE*

Abstract—A key challenge to the future of energy-harvesting systems is the discontinuous power supply that is often generated. We propose a new approach, Hibernus, which enables computation to be sustained during intermittent supply. The approach has a low energy and time overhead which is achieved by reactively hibernating: saving system state only once, when power is about to be lost, and then sleeping until the supply recovers. We validate the approach experimentally on a processor with FRAM nonvolatile memory, allowing it to reactively hibernate using only energy stored in its decoupling capacitance. When compared to a recently proposed technique, the approach reduces processor time and energy overheads by 76-100% and 49-79% respectively.

Index Terms—energy harvesting, checkpointing, embedded software

### I. INTRODUCTION

Energy-harvesting systems power themselves by extracting energy from the environment [1]. However, the energy provided is often highly temporally dynamic, providing an intermittent supply that is incapable of sustaining computation. This is because processors switch off when the supply drops below their minimum operating voltage and, when power is available again, restart computation from the beginning.

To manage an intermittent supply, one approach is to use a battery or supercapacitor to buffer energy. However, the level of miniaturisation required to realise medical implants [2] or visions of 'smart dust' [3] causes energy storage to be minimised, constraining the computational ability of systems. Recently, a different approach (Mementos [4]) was proposed, which uses the well-known concept of checkpoints [5] placed at compile-time. Mementos saves periodic snapshots of system state to non-volatile memory (NVM), which enable it to return to a previous checkpoint after a power failure. A number of checkpoint placement heuristics are proposed, including at the beginning of every function-call or before any loop. At runtime, when these checkpoints are reached, the supply voltage  $(V_{\rm CC})$  of the processor is inspected using the an analog-todigital converter (ADC). If it is deemed to be failing ( $V_{CC}$  < a threshold  $V_{\rm M}$ ), a snapshot of the system state is saved to NVM. This requires regular polling of the supply voltage, and can result in multiple snapshots being saved when the

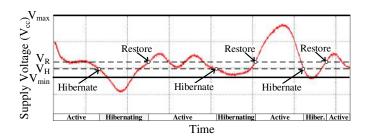

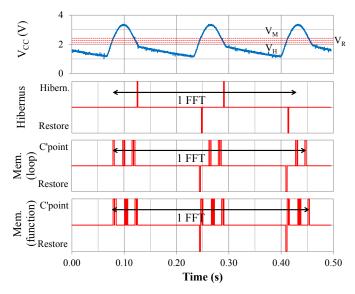

Fig. 1. Operation of Hibernus in response to intermittent supply voltage.

supply voltage is close to the threshold; both introduce time and energy overheads.

This brief proposes *Hibernus*<sup>1</sup>, a new approach which automatically saves a snapshot only once (without the need for checkpoint placement heuristics), immediately before power failure, then sleeps. *Hibernus* saves the system's complete volatile memory; this is enabled in part by developments in Ferroelectric RAM (FRAM), a NVM technology that is more efficient than flash, and is now being monolithically integrated into low-power microcontrollers [6]. The speed and efficiency of integrated FRAM means we can react to power loss and save a snapshot using only the energy stored in a system's decoupling capacitance.

# II. HIBERNUS

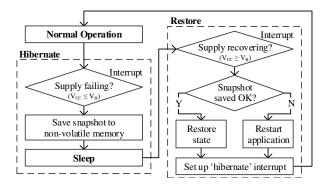

The *Hibernus* approach has two states: active and hibernating. It moves between these states when the supply voltage ( $V_{\rm CC}$ ) passes thresholds (Fig. 1). It uses a hardware interrupt to detect when  $V_{\rm CC}$  drops below  $V_{\rm H}$ , then prompts a reactive hibernation – saving an immediate snapshot of volatile memory, then entering deep sleep. The snapshot is restored by another interrupt, when the supply voltage rises above  $V_{\rm R}$ . The approach is illustrated in Fig. 2 and differs from Mementos, whose checkpoint locations are set in advance. Due to this, our approach is more energy- and time-efficient than existing approaches (experimentally demonstrated in Sec. III), and does not depend on checkpoint placement heuristics.

Hibernus is application-agnostic and transparent to the programmer, because it can reactively hibernate at any time during the execution of an application. Therefore, to save a snapshot of system state, it copies all registers and volatile memory to NVM. The energy consumed by this process,  $E_{\sigma}$ ,

© 2014 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

D. Balsamo, A. S. Weddell, G. V. Merrett and B. M. Al-Hashimi are with the Pervasive Systems Centre, Electronics and Computer Science, University of Southampton, UK.

D. Brunelli is with the Department of Industrial Engineering, University of Trento, Italy.

D. Balsamo and L. Benini are with the Department of Electrical, Electronic and Information Engineering "Guglielmo Marconi" (DEI), University of Bologna Italy

$<sup>^{1}</sup>$ In computing, 'hibernation', from the Latin  $h\bar{\imath}bernus$ , is the process of saving state to allow power to be removed.

Fig. 2. Flow-chart illustrating the Hibernus approach.

depends on the size of the volatile memory and the energy consumption for copying each byte.

$$E_{\sigma} = n_{\alpha} E_{\alpha} + n_{\beta} E_{\beta} \tag{1}$$

Here,  $n_{\alpha}$  and  $n_{\beta}$  are the sizes of the RAM and registers (in bytes).  $E_{\alpha}$  and  $E_{\beta}$  are the energy required to copy each RAM and register byte to NVM (J/byte).

Hibernus requires sufficient NVM to save the contents of all processor registers and RAM. This is the case with modern microcontrollers, e.g. [6]. It also requires enough energy to be stored in the capacitance between the supply rails to save a full snapshot. Energy harvesting systems normally operate across a range of voltages, from  $V_{\min}$  to  $V_{\max}$ . Below  $V_{\min}$ , processors may operate unpredictably (brown-out), or shut down completely. Given the total capacitance  $(\sum C)$ , the energy  $E_{\delta}$  stored between a given voltage V and  $V_{\min}$  is:

$$E_{\delta} = \frac{V^2 - V_{\min}^2}{2} \cdot \sum C \tag{2}$$

To ensure stability,  $V_{\rm H}$  is set so that  $E_{\sigma} > E_{\delta}$ , to enable complete hibernation (even with a sudden loss of supply).  $V_{\rm R}$  is set higher to add hysteresis, allowing the system to restore without taking the  $V_{\rm cc}$  below  $V_{\rm H}$ , even with sudden loss of supply. For small embedded microcontrollers (with relatively small  $n_{\alpha}$ ) using fast-write NVM (therefore relatively low  $E_{\alpha}$ ), it is possible to save a snapshot without additional C (using only the system's decoupling capacitance); this is explored in Sec. III. However, if  $E_{\delta} < E_{\sigma}$  with  $V = V_{\rm max}$ , it will not be possible to guarantee that snapshots can be taken reliably, and extra C must be added.

The total time,  $T_{\rm hibernus}$ , to execute a test algorithm with Hibernus is given by (3), where  $T_a$  is the CPU time required to execute the algorithm,  $n_t$  is number of power interruptions (where  $V_{\rm CC} < V_{\rm min}$ ) per algorithm execution,  $T_s$  is the time required to save a snapshot to NVM,  $T_r$  is the time required to restore from NVM memory, and  $\overline{T}_{\lambda}$  is the average time spent sleeping (after a snapshot has been saved but before  $V_{\rm cc} = V_{\rm min}$ , and on power-up when  $V_{\rm min} < V_{\rm CC} < V_{\rm R}$ ). The absolute limit of supply interruption frequency,  $f_t$ , is  $1/(T_s + T_r)$ .

Algorithm Save snapshot Sleep

$$\underline{T_{\text{hibernus}}} = T_a + \underline{n_\iota} \left( T_s + \underline{T_r} + \overline{T_\lambda} \right)$$

Total execution No. interruptions Restore snapshot (3)

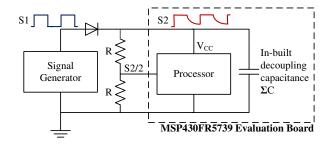

Fig. 3. The test platform used to experimentally validate Hibernus.

The total time,  $T_{\rm mementos}$ , to execute an algorithm with Mementos is given by (4), where  $n_m$  is the number of checkpoints per complete execution of the algorithm,  $T_m$  is the time taken for an ADC reading of  $V_{\rm CC}$ , and  $P_s$  is the proportion of checkpoints resulting in a snapshot, taking  $T_s$ .

$$\underbrace{T_{\text{mementos}}}_{\text{Total execution}} = \underbrace{T_a}_{\text{No. interruptions}} + \underbrace{n_\iota \left(T_r + \frac{T_a}{2n_m}\right)}_{\text{Resktrack}} + \underbrace{n_n \left(T_m + P_s T_s\right)}_{\text{Backtrack}} (4)$$

Hence,  $T_{\rm hibernus} < T_{\rm mementos}$  provided  $n_{\iota}(T_a/2n_m) + n_m T_m + (n_m P_s - n_{\iota}) T_s > n_{\iota} \overline{T_{\lambda}}$ ; that is, *Hibernus* spends less time sleeping than Mementos spends on backtracks (rerunning code that was executed between a snapshot and a power interruption), sampling  $V_{\rm cc}$ , and redundant snapshot saves. This is evaluated experimentally in the next section.

### III. EXPERIMENTAL VALIDATION

*Hibernus* has been validated with an intermittent power supply and representative workload. Its energy and time overheads have been evaluated, and compared against Mementos.

### A. Implementing Hibernus

While most microcontrollers have flash NVM (and consequently a high  $E_{\sigma}$ ), processors are emerging that incorporate fast, low-power FRAM (and hence have a lower  $E_{\sigma}$ ). The test platform (Fig. 3) uses a development board combining a Texas Instruments MSP430 processor [6] with FRAM. This means that its decoupling capacitance alone allows  $E_{\delta} >> E_{\sigma}$  when  $V=V_{\rm max}$ , requiring no additional energy storage (battery or large capacitor) to support *Hibernus*. The approach will work with platforms with flash memory rather than FRAM, but this will significantly reduce the maximum supply interruption frequency and increase the energy overhead, potentially requiring additional capacitance on the supply.

The platform's datasheet parameters were inspected, and identified  $E_{\alpha}$  as 4.2 nJ/byte and  $E_{\beta}$  as 2.7 nJ/byte, with a total RAM size of 1024 bytes and register size of 524 bytes. The platform operates with a  $V_{\rm max}=3.6~V$  and  $V_{\rm min}=2.0~V$ . Using (1), a complete operation copying all registers and RAM to FRAM consumes 5.7  $\mu$ J. The decoupling capacitance on the board totals  $\sum C=16~\mu$ F. Using (2), it was found that this alone is sufficient for *Hibernus* and  $V_{\rm H}$  was set to 2.17 V. It was verified experimentally that this and  $V_{\rm R}=2.27~{\rm V}$  delivered stable operation, even with sudden loss of supply at

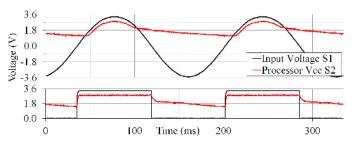

Fig. 4. Measured behavior of signals S1 and S2 (Fig. 3) with (a) 6 Hz square-wave input; (b) 6 Hz sinusoidal input.

the beginning of a restore operation. The stability of the system is therefore unaffected by the dynamics of the power source. The test platform's  $V_{\rm CC}$  input (S2) is connected to the output of a signal generator (S1) through a diode, which prevents backflow of charge to the harvester (Fig. 3). The signal generator was selected to mimic a voltage-dominant source such as a typical RFID reader [4]. Traces (Fig. 4) with a peak amplitude of 3.6V are presented as examples. The slower decay of S2 compared to S1 is due to the input diode; the slow decay on the negative edge illustrates the discharge of the decoupling capacitance by the current drawn by the processor.

Hibernus functionality is contained within hibernus.h library file; application developers only include this library and call the initialise(), hibernate() and restore() routines, as illustrated in Fig. 5. As shown in Fig. 2, the algorithm requires that interrupts are generated when  $V_{cc}$  passes  $V_{H}$  and  $V_{R}$ ; this is facilitated by comparators and voltage references. The test microcontroller has an on-chip comparator configured with an on-chip variable reference voltage generator (these are standard features on many microcontrollers), and an external voltage divider ( $R = 200 \text{ k}\Omega$ ) giving  $V_{cc}/2$ , as inputs. This is set up in the initialise() routine. Dependent on whether the system is hibernating or active, the interrupt is set to trigger off either  $V_{\rm cc} \leq V_{\rm H}$  or  $V_{\rm cc} \geq V_{\rm R}$ . The handler then calls hibernate() or restore().

When hibernate() (Fig. 2) is called, it first pushes the core registers onto the FRAM memory. It then copies the entire RAM contents (stack segment, local and global variables) into the FRAM, followed by the general registers, and finally the Stack Pointer (SP) and Program Counter (PC). It then sleeps in a low-power mode. The system remains in sleep mode until  $V_{\rm CC} > V_{\rm R}$ . The restore() routine is then called and the complete previous system state is restored. The system phases the restore of the memory locations to reinstate its operating state reliably. The general registers are restored first, followed by the RAM, and lastly the core registers including the SP and PC. When the PC is restored from the snapshot, the system implicitly transfers to the application and resumes operation.

### B. Experimental Setup

The evaluation test case represents a common long-running task for energy harvesting systems: a Fast Fourier Transform (FFT) analysis of three arrays, each holding 128 8-bit samples of tri-axial accelerometer data. The FFT algorithm was chosen

```

#include "hibernus.h"

int main (void) {

if (flag) restore(); //restore system state

else initialise(); //initialise hibernus

// application code goes here

}

__interrupt void COMP_D_ISR(void) {

hibernate(); //save system state & sleep

}

```

Fig. 5. Example code used for evaluation of Hibernus.

as an illustration: *Hibernus* is application-agnostic and will provide the same functionality to any embedded program, with minimal impact on the application developer (see Fig. 5). Supply interruption frequencies  $f_{\iota}$  (of 2, 4, 6, 8, 10 Hz, and DC) were chosen to represent the intermittent power output that may be expected from an energy harvester (e.g. micro wind turbine or RFID inductive power transfer). This has allowed *Hibernus*' overheads to be compared against Mementos. Due to the low output impedance of the signal generator, which allows the target voltage to be attained very quickly (figs. 3 and 4), and low current draw of the microcontroller,  $f_{\iota} > 10$ Hz results in the system being continuously powered.

Our implementation of Mementos places static checkpoints after function calls or before loops, referred to as 'function' and 'loop'. ADC ( $V_{\rm cc}$ ) measurements are taken and compared to a threshold ( $V_{\rm m}=2.5V$ ), chosen for each scheme to ensure that a snapshot can be saved at least once before power failure. At each checkpoint,  $V_{\rm cc} < V_{\rm m}$  indicates imminent power failure, and a snapshot is saved. Mementos consumes energy for multiple checkpoints, both for ADC readings and saving snapshots. In contrast, *Hibernus* consumes energy for a single hibernation per power-outage, plus the quiescent consumption of the voltage reference and comparator.

The power consumption at mid-range between  $V_{\rm max}$  and  $V_{\rm min}$  of the FFT algorithm (without *Hibernus* or Mementos running), ADC, voltage reference, and comparator were measured as 2.7 mW, 310  $\mu$ W, 17  $\mu$ W and 130  $\mu$ W respectively. These values are used to estimate the energy consumption of the different approaches. For each of the three schemes, and at each frequency  $f_{\iota}$ , we evaluated: (1) the number of system restores required to complete the computation of the FFT algorithm, (2) the number of times snapshots were stored, or checkpoints were called, (3) the energy overhead, and (4) the processor time overhead. The results were averaged over three complete executions of the test program. The overheads are evaluated with reference to the time and energy for the processor to complete the FFT algorithm with a steady supply: without Mementos or *Hibernus*, it completed in 100 ms.

## C. Results

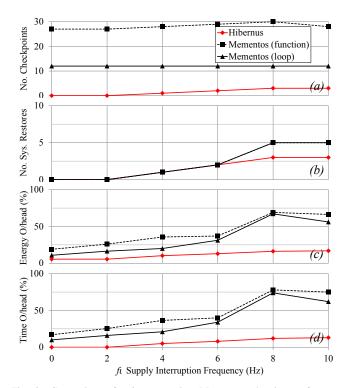

Fig. 6(a) shows how many checkpoints were made by *Hibernus* and Mementos during a single execution of the FFT. As can be seen, *Hibernus* reduces the number of times that checkpoints are taken. This can also be seen from Fig. 7, which

Fig. 6. Comparison of *Hibernus* against Mementos, showing performance when running the FFT text program (averaged over 3 executions): (a) number of checkpoints/snapshot saves, (b) number of times snapshots were restored, (c) energy overhead, (d) time overhead.

Fig. 7. Results comparing when *Hibernus* and Mementos hibernate, checkpoint, and restore. Results shown were measured over a complete execution of the test FFT algorithm, powered by a sinusoidal supply with  $f_{\iota}$  = 6 Hz.

shows when *Hibernus* and Mementos checkpoint (for the case when  $f_{\iota}=6$  Hz), whereas *Hibernus* snapshots (hibernates) only once per interruption (twice in total), Mementos executes a static number of checkpoints (12 and 27 times), although some are repeated when  $V_{\rm CC} < V_{\rm min}$  during a snapshot.

Fig. 6(b) shows that, at higher  $f_{\iota}$  values, *Hibernus* completes execution of the FFT over fewer power interruptions (3, instead of 5). This is because the mean processor time overheads (Fig. 6(d)) of *Hibernus* are 80-100% shorter than

TABLE I

EXPERIMENTALLY MEASURED PARAMETERS (SEE EQUATIONS (3), (4)).

| $f_{\iota}$ | T <sub>a</sub> | $T_s$ | Τ,   | $T_m$ | $T_{\lambda}$ | Hib.    | Loop        |       |       | Function    |       |       |

|-------------|----------------|-------|------|-------|---------------|---------|-------------|-------|-------|-------------|-------|-------|

| (Hz)        | (ms)           | (ms)  | (ms) | (ms)  | (ms)          | $n_{i}$ | $n_{\iota}$ | $n_m$ | $P_s$ | $n_{\iota}$ | $n_m$ | $P_s$ |

| 0           | 100            | 2.85  | 2.2  | 0.65  | -             | -       | -           | 12    | 0.00  | -           | 27    | 0.00  |

| 2           | 100            | 2.85  | 2.2  | 0.65  | 17            | 0       | 0           | 12    | 0.08  | 0           | 27    | 0.11  |

| 4           | 100            | 2.85  | 2.2  | 0.65  | 9.5           | 1       | 1           | 12    | 0.25  | 1           | 27    | 0.19  |

| 6           | 100            | 2.85  | 2.2  | 0.65  | 6.5           | 2       | 2           | 12    | 0.50  | 2           | 27    | 0.33  |

| 8           | 100            | 2.85  | 2.2  | 0.65  | 3.8           | 3       | 5           | 12    | 1.00  | 5           | 27    | 0.70  |

| 10          | 100            | 2.85  | 2.2  | 0.65  | 2.8           | 3       | 5           | 12    | 0.83  | 5           | 27    | 0.67  |

Mementos (function), and 76-100% shorter than Mementos (loop); this leaves more time to execute the application (also shown in Fig. 7, where the arrows denote the total execution time). Furthermore, Fig. 6(c) shows that the energy overheads of running *Hibernus* are 65-79% lower than Mementos (function) and 49-76% lower than Mementos (loop).

The benefits of *Hibernus* are most noticeable at  $f_{\iota}=0$  Hz (i.e. DC, when  $V_{\rm cc}$  is uninterrupted), where negligible time and energy overheads are imposed (see Fig. 6(c) and (d)), while Mementos still requires the same number of checkpoints. This increases the required processor active time and energy by at least 10% and 11% respectively. Table I shows experimentally obtained values for the parameters of (3) and (4). Evaluating these equations support our measured results, and confirm that *Hibernus* spends less time sleeping than Mementos spends on redundant snapshot saves, backtracks, and sampling  $V_{\rm cc}$ .

### IV. CONCLUSIONS

A new approach for sustaining computation during intermittent supply, *Hibernus*, has been proposed. This allows a system to sustain computation through power outages which are common in energy-harvesting systems. It has a lower energy and time overhead than a recently proposed scheme, as demonstrated experimentally. This contributes to the development of future energy harvesting systems. Our continuing work is investigating performance with real energy harvesters, rather than the voltage-dominant sources evaluated here.

### ACKNOWLEDGMENT

This work is part of the PRiME programme: EPSRC grant EP/K034448/1 (www.prime-project.org). It was also supported by a Telecom Italia s.p.a. PhD grant, and PHIDIAS, an EU 7th Framework Programme project (CA 318013).

### REFERENCES

- P. D. Mitcheson *et al.*, "Energy Harvesting From Human and Machine Motion for Wireless Electronic Devices," *Proc. IEEE*, vol. 96, no. 9, pp. 1457-1486, Sept. 2008.

- [2] M. R. Mhetre et al., "Micro energy harvesting for biomedical applications: A review," Proc. ICECT 2011, vol. 3, pp. 1-5, 8-10 April 2011.

- [3] B. A. Warneke and K. S. J. Pister, "An ultra-low energy microcontroller for Smart Dust wireless sensor networks," *Proc. IEEE ISSCC 2004*, pp. 316-317, vol. 1, Feb. 2004.

- [4] B. Ransford et al., "Mementos: System Support for Long-Running Computation on RFID-Scale Devices," ASPLOS11, Newport Beach, CA, USA, Mar. 5-11, 2011.

- [5] P. A. Bernstein et al., "Concurrency Control and Recovery in Database Systems," Addison-Wesley Longman Publishing, Boston, USA 1987.

- [6] M. Zwerg et al., "An 82µA/MHz microcontroller with embedded FeRAM for energy-harvesting applications," Proc. IEEE ISSCC 2011, pp.334-336, 20-24 Feb. 2011.